ようやく、SDRAMのテストを開始、結線は多いが、高速な大容量外部

メモリを得られる。

デバイスだけでも512Kバイトのメモリーを持っているので、通常は十

分ではあるけど、このようなデバイスじゃないと、SDRAMを制御する

為のハードウェアーを内臓していない、又、169ピンのデバイスじゃな

いと、32ビットの外部バスをサポートしていない。

※最大のパフォーマンスを得たいので32ビットバスで動かしてみたい。

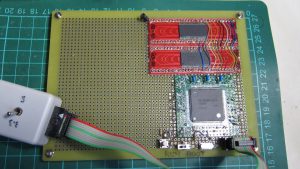

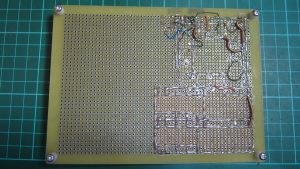

普通は、基板を起こすべきなのだろうけど、実験ではそうもいかない。

と、言っても最近では、海外のメーカーに発注すれば、基板を新規に作成

するコストは尋常じゃ無く安いので、いきなり基板を起こしてみるのも悪

くないかもしれない。

クロックが高いので、手配線では動作が難しいかもしれないが、バスに接

続するSDRAMは、CPUの動作速度の半分でしかないので、(およそ

60MHz)このくらいなら、手配線でも何とか動作すると思う。

「反射」が起こって動作が不安定になった場合は、ダンピング抵抗を調整

してインピーダンスの整合を行えば、何とかなるのでは無いかと考えてい

る。

※変換基板では、電源ラインが相対的に弱くなるのが多少気になる。

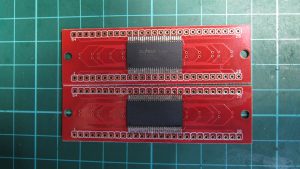

デバイスは300円(128メガビット)なのに、変換基板(Aitendo 産)

が250円するけど、他に、収まりが良く、スペースが少ない変換基板が

無かった。

※基板を起こす時には256メガビット品を使うと思うが、組み込み用途

のSDRAMを単体で入手(秋葉原などで)できるのは限られている。

最近は、0.5mmピッチのハンダ付けが多かったので、0.8mmピッ

チは、凄く楽だったーー

変換基板には、何故か余分な部分があるので、カットして、裏面にある謎

の端子パッドも、いつものようにポリイミドテープで絶縁、ベース基板と

直接コンタクトさせる。

※ピン番号のシルクが一部間違っている・・(28、29ではなく、27、

28ね・・)

※ポリイミドテープの存在を知らない時は、「紙」を貼っていた。www

まず、電源ラインを配線してから、十分なパスコンを接続、それから配線

を行った、データバスは、液晶を接続するのにも使うので、別途、コネク

ターに出す。

・電源の配線

厄介なのは、SDRAMの場合、初期化処理を行わないと、使う事ができな

い点で、それなりのパラメーターがある、とりあえず、ベストな設定より、

必ず動作しそうな無難な設定を考えてみた。

後は、SDRAMのマニュアルと、RX64Mのマニュアルを見ながら、行

い、とりあえず、書いたデータを読み出せた~

※もっと苦労すると思っていたので、意外な感じはあるが、メモリー空間は

32メガバイトもあるので、詳細なテストを行わないと、分からない。

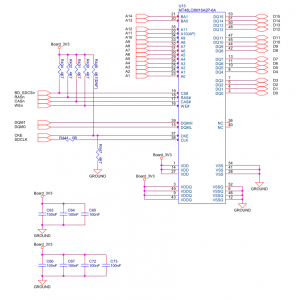

バス・インターフェースの初期化

// SDRAM 初期化 128M/32bits bus

device::MPC::PFAOE0 = 0xff; // A8 to A15

device::MPC::PFBCR0 = device::MPC::PFBCR0.ADRLE.b(1) |

device::MPC::PFBCR0.DHE.b(1) |

device::MPC::PFBCR0.DH32E.b(1);

device::MPC::PFBCR1 = device::MPC::PFBCR1.MDSDE.b(1) |

device::MPC::PFBCR1.DQM1E.b(1) |

device::MPC::PFBCR1.SDCLKE.b(1);

device::SYSTEM::SYSCR0 = device::SYSTEM::SYSCR0.KEY.b(0x5A) |

device::SYSTEM::SYSCR0.ROME.b(1) |

device::SYSTEM::SYSCR0.EXBE.b(1);

while(device::SYSTEM::SYSCR0.EXBE() == 0) asm("nop");

SDRAM の初期化

device::BUS::SDIR = device::BUS::SDIR.ARFI.b(0) |

device::BUS::SDIR.ARFC.b(1) |

device::BUS::SDIR.PRC.b(0);

device::BUS::SDICR = device::BUS::SDICR.INIRQ.b(1); // 初期化シーケンス開始

while(device::BUS::SDSR() != 0) asm("nop");

// 動作許可、32ビットアクセス

device::BUS::SDCCR = device::BUS::SDCCR.BSIZE.b(1);

// Burst read and burst write, CAS latency: 3, Burst type: Sequential, Burst length: 1

device::BUS::SDMOD = 0b00000000110000;

// CAS latency: 3, Write recovery: 1, ROW prechage: 4, RAS latency: 3, RAS active: 4

device::BUS::SDTR = device::BUS::SDTR.CL.b(3) |

device::BUS::SDTR.RP.b(3) |

device::BUS::SDTR.RCD.b(2) |

device::BUS::SDTR.RAS.b(3);

// 128M/16 カラム9ビット、ロウ12ビット

device::BUS::SDADR = device::BUS::SDADR.MXC.b(1);

// Refresh cycle

device::BUS::SDRFCR = device::BUS::SDRFCR.RFC.b(2048) |

device::BUS::SDRFCR.REFW.b(7);

device::BUS::SDRFEN = device::BUS::SDRFEN.RFEN.b(1);

// SDRAM 動作開始

device::BUS::SDCCR.EXENB = 1;